### New Languages for High Performance Computing

Iris Christadler, Leibniz Supercomputing Centre, Germany August 2010, PDC/KTH Summer School

### **Outline**

- The free lunch is over Multicore CPUs are ubiquitous

- 2. Hardware accelerators

New languages enter the HPC world

- The quest for a parallel language Examples of emerging languages

### The free lunch is over

"But if you want your application to benefit from the continued exponential throughput advances in new processors, it will need to be a well-written concurrent application. And that's easier said than done, because not all problems are inherently parallelizable and because concurrent programming is hard."

#### The Free Lunch Is Over

A Fundamental Turn Toward Concurrency in Software

By Herb Sutter

[http://www.gotw.ca/publications/concurrency-ddj.htm]

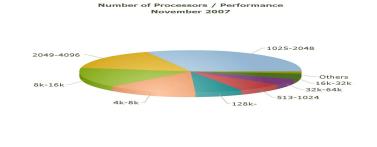

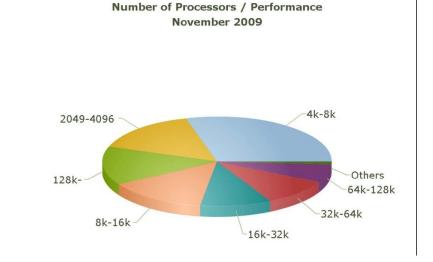

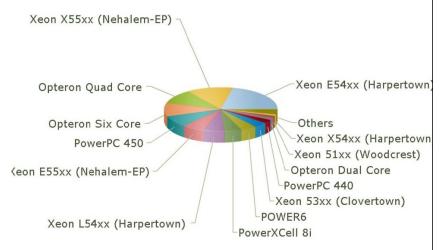

### top500.org

mages: www.top500.org

New Languages for High Performance Computing, Iris Christadler, LRZ August 2010

Itanium 2

# L<sub>TZ</sub>

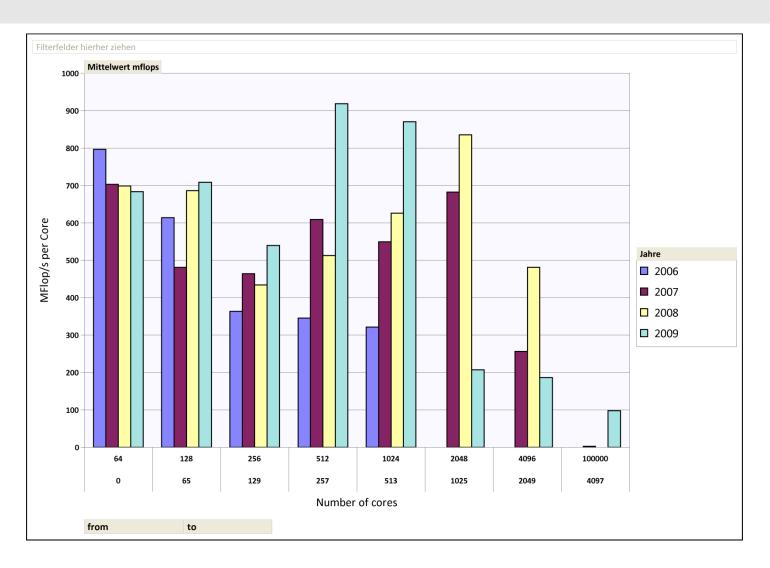

### LRZ's job mix

Performance per core versus number of cores

### My favorite "Dongarra" slides

[http://www.netlib.org/utk/people/JackDongarra/SLIDES/dongarra-isc2004.pdf] [http://www.netlib.org/utk/people/JackDongarra/SLIDES/sc09-exascale-panel.pdf]

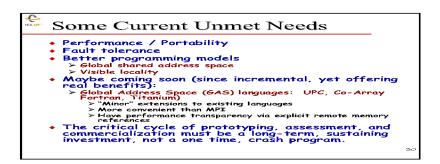

# Real Crisis With HPC Is With The Software Programming is stuck Arguably hasn't changed since the 70's It's time for a change Complexity is rising dramatically highly parallel and distributed systems From 10 to 100 to 1000 to 10000 to 10000 of processors! Mutidisciplinary applications A supercomputer application and software are usually much more long-lived than a hardware Hardware life typically five years at most. Fortran and C are the main programming models Software is a major cost component of modern technologies. The tradition in HPC system procurement is to assume that

#### IESP: The Need

- The largest scale systems are becoming more complex, with designs supported by consortium

- □ The software community has responded slowly

- Significant architectural changes evolving

- Software must dramatically change

- Our ad hoc community coordinates poorly, both with other software components and with the vendors

- Computational science could achieve more with improved development and coordination

### A Call to Action

- Hardware has changed dramatically while software ecosystem has remained stagnant

- Previous approaches have not looked at co-design of multiple levels in the system software stack (OS, runtime, compiler, libraries, application frameworks)

- Need to exploit new hardware trends (e.g., manycore, heterogeneity) that cannot be handled by existing software stack, memory per socket trends

- Emerging software technologies exist, but have not been fully integrated with system software, e.g., UPC, Cilk, CUDA, HPCS

- Community codes unprepared for sea change in architectures

- No global evaluation of key missing components

www.exascale.org

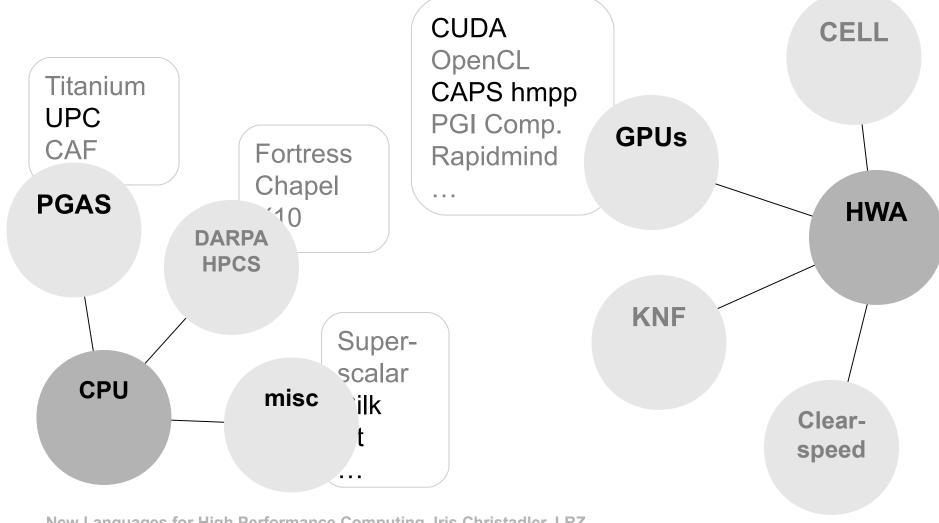

New languages enter the HPC world

### Hardware Accelerators

## Hard

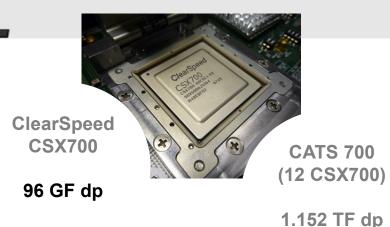

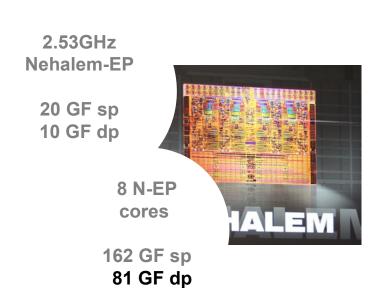

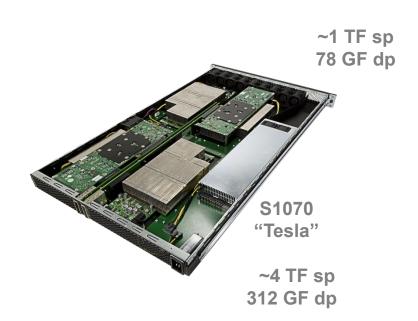

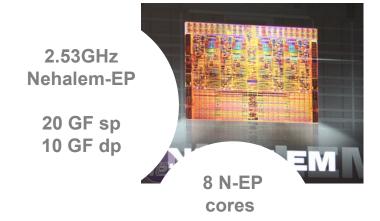

### Hardware in 2008/9

410 GF sp 205 GF dp

C1060 GPU

### Hardware 2010

Intel MIC architecture "Knights Ferry"

http://download.intel.com/pressroom/archive/reference/ISC\_2010\_Skaugen\_keynote.pdf

32 cores @ 1.2 GHz 4 threads/core 8 MB shared coherent cache 1-2 GB GDDR5

"Knights corner"

1st MIC product

22nm process >50 cores

162 GF sp 81 GF dp C2070 GPU

1.0 TF sp 0.5 TF dp

\$2070 "Fermi"

4 TF sp 2 TF dp

NVIDIA Tesia S2070 (Quelle: NVIDIA)

### Pros and Cons for HWA

### Pros:

- HWA can help to tackle research problems

(in many cases they are simply less expensive than traditional solutions)

- HWA help to shrink the physical footprint of systems

- HWA can help to reduce the power consumption both of the machine and the cooling system

### Cons:

- You need to make use of them, otherwise they simply waste energy

- HWA will probably increase the error-rate

- HWA are no solution for scalability problems

- HWA are difficult to program (?)

Examples of emerging languages

### The quest for a parallel language

# L<sub>Z</sub>

### Overview

New Languages for High Performance Computing, Iris Christadler, LRZ August 2010

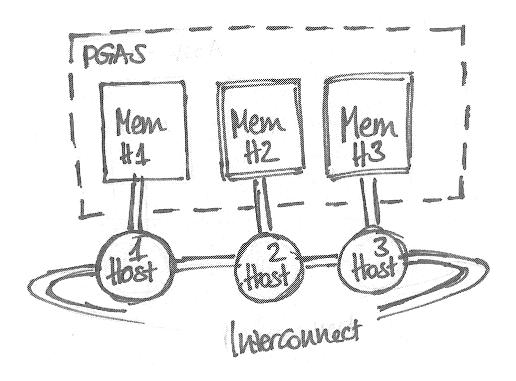

### **PGAS**

### Partitioned Global Address Space language

- The concept and it's different implementations

- UPC vs. CAF: some fundamental differences

- · Performance improvements?

- · Ease-of-use?

- Planned hardware (interconnect) support

### **UPC**

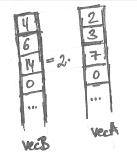

### Unified Parallel C – a PGAS example

```

# include <upc.h>

# define CHUNK (int) (N/THREADS)

shared [CHUNK] double vecA[N];

shared [CHUNK] double vecB[N];

. . .

int main () {

if (MYTHREAD == 0) {

printf("Main thread\n");

upc barrier;

upc forall (j=0; j<N; j++; &a[j]) {

vecB[j] = 2*vecA[j];

upc barrier;

```

### CUDA

### The Compute Unified Device Architecture for Nvidia GPUs

```

host code:

// allocate memory on gpu

cudaMalloc (ptr, size);

cudaMemcpy (dst, src, size, dir:host2dev);

// launch kernel

kernels

kernel<<<qridSize, blockSize>>> (funcParams);

// copy results back

cudaMemcpy (..., dir:dev2host);

cudaFree;

device code:

_global__ void kernel(float* vecA, float* vecB, int threading t width){

unsigned int x = blockIdx.x*blockDim.x + threadIdx.x;

unsigned int y = blockIdx.y*blockDim.y + threadIdx.y;

if (x < width && y < height) {

vecB[y*width+x] = 2*vecA[y*width+x];

```

- **GPGPU** programming de-facto standard

- Small lightweight

- Parallelization through hyper-threading

- Hiding cache misses and latency through

### CAPS hmpp

### GPGPU programming using simple directives

```

#pragma hmpp kernel codelet, target=CUDA,

args[vecA, height, width].io= in, args[vecB].io=inout

void kernel (float *vecA, float *vecB, int height, int width)

for (x=0; x< width; x++)

for (y= 0; y< height; y++)

What is CAPS hmpp?

vecB[y*widht+x] = 2*vecA[y*width+x];

Similar to the PGI acc.

compiler approach

Similarities with

int main() {

OpenMP

#pragma hmpp kernel allocate

Possibilities &

#pragma hmpp kernel advancedload, args[vecA, vecB, Limitations

#pragma hmpp kernel callsite &

#pragma hmpp kernel args[...].advancedload=true

kernel (vecA, vecB, height, width);

#pragma hmpp kernel release

```

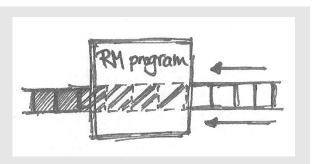

### RapidMind

as a placeholder for Intel Ct (not yet publicly released)

```

#include <rapidmind/platform.hpp>

using namespace RapidMind;

int main () {

// declaration

Array<2, Value4f> vecA;

Array<2, Value4f> vecB;

Program kernel= BEGIN {

// program definition

In<Value4f> a;

Out<Value4f> b;

b = 2*a;

END;

// program call

vecB = kernel(vecA);

```

- "Array computing"/"data stream computing"

- Intel acquired RapidMind

- RapidMind technology will be integrated in Ct

- RapidMind offered backends for: Cell, Cuda, GLSL, x86

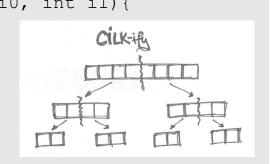

### Cilk

### automatic parallelization through recursive procedures

```

cilk double kernel(float *vecA, float *vecB, int i0, int i1) {

if ((i1-i0) == 1) {

vecB[i0] = 2*vecA[i0];

return;

else {

int im= (i0+i1) / 2;

double vecL, vecR;

vecL= spawn kernel(vecA, vecB, i0, im);

vecR= spawn kernel(vecA, vecB, im, i1);

sync;

return;

Cilk int main() {

spawn kernel(...);

sync;

```

- Automatic

parallelization and load

balancing (!) through

recursion

- Divide-and-conquer style programming

- Needs an adaptation of many algorithms

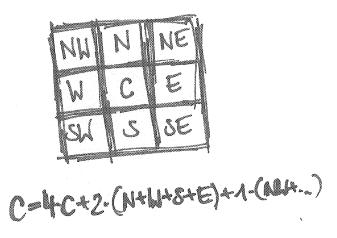

Now do this exercise for a more

### A 2D Stencil Computation

Contact details: Iris Christadler (christadler@lrz.de), LRZ, Germany

### Thank you for your attention!